Configuração do modo

O FT4222H possui 4 modos de configuração selecionados por {DCNF1, DCNF0}. O modo de configuração do chip determinará o número de interfaces USB para fluxos de dados e para o controle GPIOS. A interface de fluxo de dados é para transferência de dados entre o host USB2.0 e o dispositivo SPI / I2C. O objetivo da interface GPIO é totalmente controlar os GPIOS.

Com o módulo UMFT4222EV, o usuário pode configurar facilmente o modo de chip através de jumpers (JP2 e JP3). Por favor, consulte a Tabela 4 e 5 para detalhes. Um chip reset ou ciclismo de energia é necessário após a mudança de configuração. A tabela a seguir mostra as funções do PIN correspondente ao modo de configuração do chip.

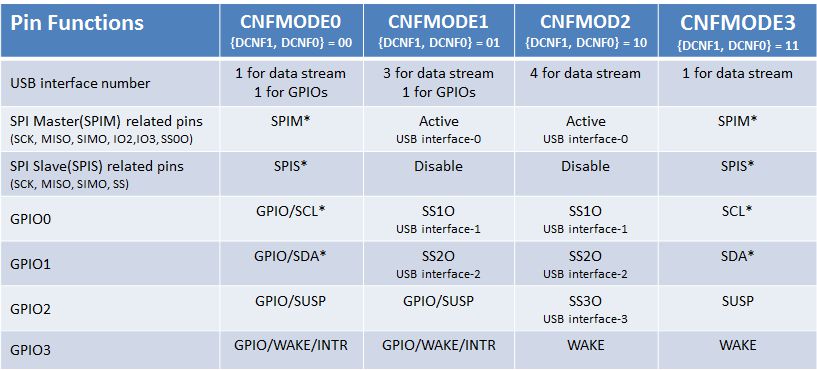

Tabela 8 FT4222H Funções do PIN no modo de configuração do chip

* Uma das funções SPIM, SPIS, I2C é selecionada, as outras 2 funções serão desativadas

Nota: O GPIO Pins não pode ser controlado pelo driver quando o GPIO PINS desempenha a função como SPIM SSXO, I2C SCL / SDA, suspeito ou acordar.

A configuração do chip determina apenas o número de interface / função suportada, mas não decide qual interface de barramento (SPI / I2C / GPIO) ou qual função (mestre / escravo) que o FT4222H tomará.

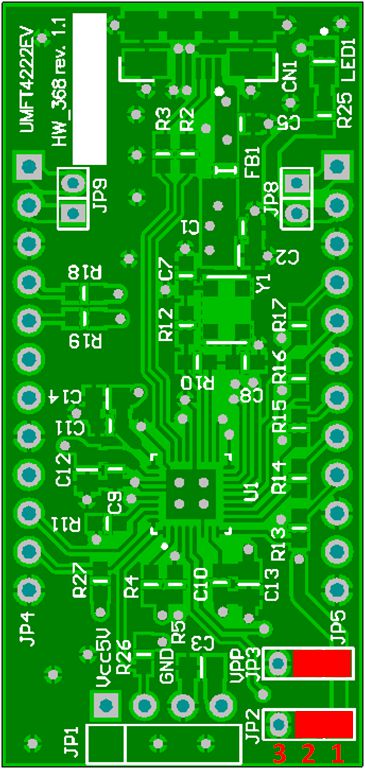

Figura 5-1 JP2 / JP3 Configuração Exemplo: Modo 3 (DCNF0 = 1, DCNF1 = 1)

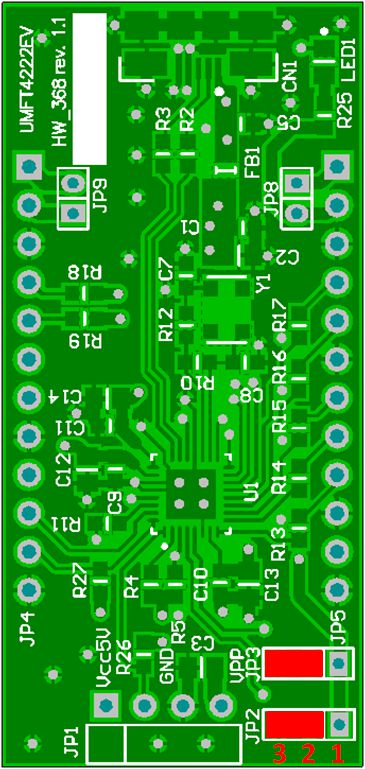

Figura 5-2 JP2 / JP3 Configuração Exemplo: Modo 0 (DCNF0 = 0, DCNF1 = 0)

Definição de Pin SPI.

A função Quadspi no FT4222H é um dispositivo mestre / escravo SPI totalmente configurável. Os usuários podem utilizar a API em libft4222, ft4222_spimaster_init ou ft4222_spislave_init, para selecionar em qual modo (mestre ou escravo) o FT4222H funcionará. Quando o FT4222H é definido como uma função de ponte USB-para-SPI, o modo de configuração do chip é escolhido, os pinos do FT4222H serão mapeados de acordo. Os pinos relacionados SPI são –

| · Clock | – SCK | JP5 pin 9. Clock output in SPI master mode. |

| It will become clock input in SPI slave mode. | ||

| · Data | – MISO | JP5 pin 8. Data transfer from slave to master for single mode. |

| It can also become data bus bit-1 for dual and quad mode. | ||

| – MOSI | JP5 pin 7. Data transfer from master to slave for single mode. | |

| It can also become data bus bit-0 for dual and quad mode. | ||

| – IO2 | JP5 pin 5. Data bus bit-2 for quad mode | |

| – IO3 | JP5 pin 4. Data bus bit-3 for quad mode |

• Seleção escrava quando o quadspi atua como mestre SPI

– SS0O JP4 PIN 9. Seleção escrava para o dispositivo escravo-0.

– SS1O JP4 PIN 4. Seleção de escravos para o dispositivo escravo – 1.

– SS2O JP4 PIN 5. Seleção de escravos para o dispositivo escravo – 2.

– PIN SS3O JP4 6. Seleção escrava para o dispositivo escravo – 3.

• Seleção escrava quando o quadspi atua como escravo SPI

– SS JP4 PIN 11. Seleção escrava para controle mestre SPI.

Este PIN deve amarrar para alto quando o quadspi atua como mestre SPI.

Definição de Pin I2C.

A função i2c no FT4222H é um dispositivo mestre / escravo I2C totalmente configurável. Quando a configuração do chip é definida como a função CNFMode0 ou CNFMode3 e CNFMODE3 e USB-TO-I2C está ativada, os pinos relacionados ao I2C do FT4222H são:

• Relógio – SCL JP4 PIN 4. É uma saída de relógio com design de drenagem aberta quando o I2C é definido como mestre. É uma entrada do relógio quando o I2C é definido como escravo.

• Dados – SDA JP4 PIN 5. É comando / endereço / transferência de dados entre o mestre e o escravo com design de drenagem aberta.

GPIO PIN Definition.

O FT4222H contém 4 pinos GPIO para várias funções. A força de condução, o controle da taxa de manípia e os resistores altos / baixos podem ser controlados.

• GPIO0 JP4 PIN 4. Este PIN pode ser configurado como GPIO0 ou I2C SCL no modo I2C ou SPI Master Mode Seleção Slave SS1O.

• GPIO1 JP4 PIN 5. Este pino pode ser configurado como GPIO1 ou I2C SDA no modo I2C ou seleção de escravo do modo mestre SPI SS2O.

• GPIO2 JP4 PIN 6. Este PIN pode ser configurado como GPIO2 ou Suspensão USB Suspender (suspensão) ou SPI Master Mode Seleção Slave SS3O.

• GPIO3 JP4 PIN 7. Este PIN pode ser configurado como GPIO3 ou USB Remote Wake-up Entrada (WORK).

Outras definições de pin

Umft4222ev contém sinais BCD_DET e redefinir # para uso do usuário.

| · BCD_DET | JP4 pin 10. | Battery charger detection asserted when the device is |

| connected to a dedicated charging port. The polarity of this | ||

| pin can be defined. | ||

| · RESET# | JP5 pin 11. | This pin used to reset the FT4222H, it is active low. |

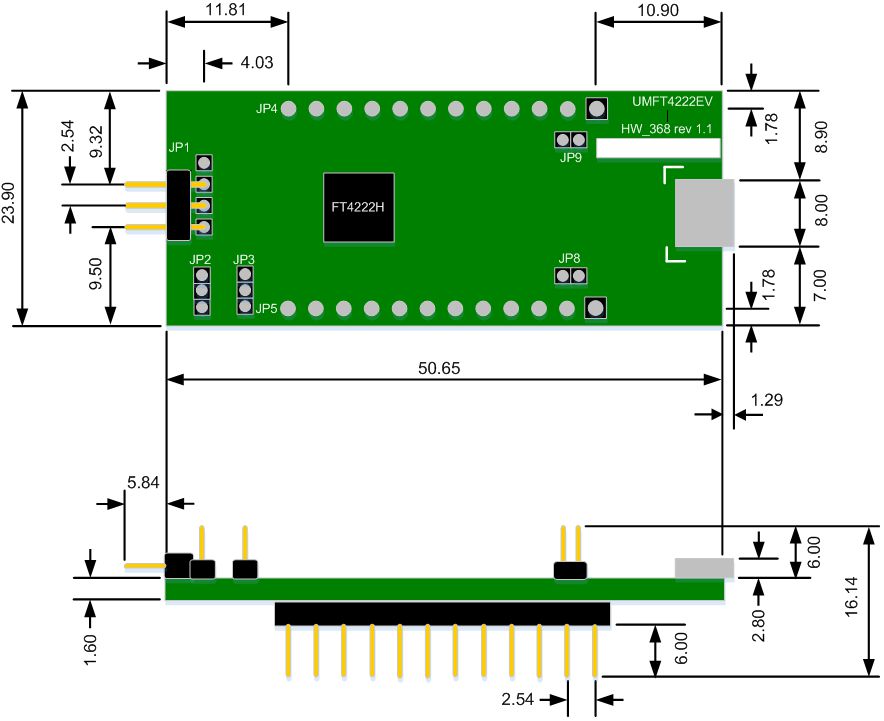

Dimensões do módulo

Dimensões do módulo UMFT422EV

Todas as dimensões são em milímetros. A tolerância é +/- 0,2mm.

Última atualização em fevereiro 16, 2024 por driverbr

Deixe um comentário