Função Descrição

O FT233HP / FT232HP é um USB 2.0 Hi-Speed (480MB / S) para UART / FIFO IC com portas USB Type-C / PD. Pode ser configurado em uma variedade de interfaces serial ou paralelas padrão da indústria, como os modos UART, FIFO, JTAG, SPI (mestre) ou I2C (mestre). Além disso, o FT233HP / FT232HP apresenta a interface FT1248 e suporta um modo FIFO estilo CPU, bit-bang e um modo de interface serial rápido.

O FT233HP possui duas portas Tipo-C / PD, com a porta PD1, suportando as funções do dissipador e da fonte de energia e a porta PD2 (somente ft233hpq e ft233hpl) trabalhando como uma porta do dissipador de energia. Ambas as portas PD suportam perfis de 5V3A, 9V3A, 12V3A, 15V3A e 20V3A PDO, e esses perfis são configuráveis através do EEPROM externo na inicialização ou redefinição. A porta PD1 compartilha o mesmo conector Tipo-C com dados USB, e a porta PD2 é apenas uma porta de energia sem dados USB.

Características principais

Controlador USB Tipo-C / PD. O FT233HP / FT232HP suporta a versão de especificação do USB Type-C 1.3. O FT233HP / FT232HP integra um controlador USB PD 3.0. USB PD Port 1 é USB PD3.0 com a função USB 2.0. A primeira potência USB PD é o dissipador de energia inicial quando a fonte de energia local é apresentada, ela pode se tornar fonte de energia via negociação de PD. O FT233HP possui uma segunda porta de dissipação USB PD para se conectar a uma fonte de energia PD. A função FT233HP / FT232HP USB PD 3.0 é compatível com o padrão USB PD 2.0.

USB Hi-Speed para Interface UART / FIFO. O FT233HP / FT232HP fornece USB 2.0 Hi-Speed (480MBits / s) para interfaces UART / FIFO flexíveis e configuráveis.

Integração funcional. O FT233HP / FT232HP integra um motor de protocolo USB que controla a interface Macrocell Universal Física Macrocell (UTMI) e lida com todos os aspectos da interface de alta velocidade USB 2.0. O FT233HP / FT232HP inclui um regulador Integrado + 1.2V Baixo Drop-Out (LDO). Também inclui buffers de dados de 1kbytes TX e RX. O FT233HP / FT232HP integra todo o protocolo USB no chip sem necessidade de firmware.

MPSSE. Motores seriais síncronos multi-protocolo (MPSSE), capazes de acelerar até 30 Mbits / s, fornece configurações flexíveis de interface síncrona.

Interface FT1248. O FT233HP / FT232HP suporta uma nova interface FT1248 semestrália proprietária com uma interface de barramento de dados bidirecional variável que pode ser configurada como 1, 2, 4 ou 8-bits de largura e isso permite a flexibilidade para expandir o tamanho dos dados ônibus para 8 pinos. Para obter detalhes sobre os modos de 2 bits, 4 bits e 8 bits, consulte a Nota de Aplicativo An_167 FT1248 Serial Paralelo Paralelo Básico.

Taxa de transferência de dados. O FT233HP / FT232HP suporta uma taxa de transferência de dados até 12 mbaud quando configurada como uma interface UART RS232 / RS422 / RS485 até 40 mbytes / segundo sobre uma interface FIFO paralela síncrona 245 ou até 8 mbyte / s acima de uma interface FIFO assíncrona 245 . Por favor, note que o FT233HP / FT232HP não suporta as taxas de transmissão de 7 mbaud 9 mbaud, 10 mbaud e 11 mbaud.

Temporizador de latência. Um recurso do driver usado como um tempo limite para transmitir pacotes curtos de dados de volta ao PC. O padrão é 16ms, mas pode ser alterado entre 1ms e 255ms.

Funcionalidade de ônibus (acbus), inversão de sinal e seleção de resistência à unidade. Existem 11 pinos de E / S configuráveis da ACBUS. Essas opções configuráveis são:

1. Txden – transmitir Ativar para projetos RS485.

2. PWREN # – Controle de energia para poder de alta potência, desenhos movidos a ônibus.

3. Txled # – para pulsar um LED após a transmissão de dados.

4. RXLED # – para pulsar um LED após receber dados.

5. TX & RXLED # – O que pulsará um LED após a transmissão ou a recepção de dados.

6. Sleep # – indica que o dispositivo entrando para o modo de suspensão USB.

7. CLK30 / CLK15 / CLK7.5 – 30MHz, 15MHz e opções de sinal de saída de relógio de 7.5MHz.

8. Trist-PU – Entrada puxada para cima, não usada

9. Drive 1 – saída de saída de alta

10. Drive 0 – saída de condução baixa

11. Modo de E / S – ACBUS Bit Bang

Os pinos da ACBUS também podem ser configurados individualmente como Pinos GPIO, semelhantes ao modo de bang assíncrono. É possível usar este modo enquanto a interface UART estiver sendo usada, fornecendo até 4 pinos de E / S de finalidade geral (ACBUS 5, 6, 8 e 9) que estão disponíveis durante a operação normal. As linhas ACBUS podem ser configuradas com qualquer uma dessas opções de entrada / saída, definindo bits no EEPROM externo.

Descrições de bloco funcional

Tipo-c / pd phy e controlador. O FT233HP (ft233hpq e ft233hpl only) possui duas portas tipo C / PD. Cada porta tem a camada física do tipo C / PD requerida (phy) e controladores. A porta PD1 possui interruptores VCONN integrados suportando até 100MW VConn Power.

Motor de política de PD. O mecanismo de política PD é um processador 32bit RISC com RAM de dados 8KB e ROM de 48KB. Ele gerencia tanto o PD Port 1 quanto a porta 2. As configurações PD padrão são armazenadas no código-ROM. A porta PD1 pode atuar como pia de potência ou função de origem, suportando a troca de função normal de energia. Porta PD2 (somente FT233HPq e FT233HPL) atua como pia de energia, que pode ser conectado a um carregador de PD. Ao usar um EEPROM externo, é possível alterar a configuração do PD com base em casos de uso específicos, como a pia da porta 1, a porta 1 pia / azedo CE ou PD Carregou da porta 2 para a porta 1. PDO Tensão / Perfis de corrente também podem ser personalizados usando EEPROM.

Interface de escravo i2c. O aplicativo também pode optar por controlar a política do PD por MCU externo por meio da interface I2C. Neste caso, o mecanismo de política PD integrado é interrompido. O MCU externo tem controle total para os dois registros do PD Controller (somente FT233HPQ e FT233HPL apenas) por meio do I2C. Um sinal de interrupção também é fornecido, de modo que uma interrupção para uma MCU externa pudesse ser declarada quando ocorrer um evento PD.

Bloco gpio. O bloco GPIO fornece até 8 pinos GPIO, que podem ser usados como controles de chave de energia com base na política e perfis PD.

Controladores UART / FIFO multi-propósito. O FT233HP / FT232HP possui um controlador independente UART / FIFO. Isso controla os dados do UART, 245 dados FIFO, o modo de serial rápido (isolamento opto) ou bit-bang que podem ser selecionados pelo comando SETUP (FT_SETBITMODE). Cada controlador UART / FIFO multi-propósito também contém um MPSSE (mecanismo serial síncrono multi-protocolo). Usando este MPSSE, o controlador UART / FIFO multi-propósito pode ser configurado em comando de software, para ter um dos MPSSE (SPI (mestre), I2C e jtag).

Motor de protocolo USB e controle FIFO. O protocolo USB controla e gerencia a interface entre o UTMI PHY e os FIFOS do chip. Também lida com o gerenciamento de energia e a especificação do protocolo USB.

Porta FIFO TX Buffer (1kbytes). Os dados do PC Host são armazenados nesses buffers a serem usados pelos controladores UART / FIFO multiusos. Isso é controlado pelo motor de protocolo USB e no bloco de controle FIFO.

Porta FIFO RX Buffer (1kbytes). Os dados dos controladores UART / FIFO multi-propósito são armazenados nesses blocos a serem enviados de volta ao PC Host quando solicitado. Isso é controlado pelo motor de protocolo USB e no bloco de controle FIFO.

Redefinir Generator – A célula do gerador de redefinição integrada fornece uma redefinição de energia confiável para o circuito interno do dispositivo na inicialização. A entrada de redefinição (com largura de pulso min) permite que um dispositivo externo redefina o FT233HP / FT232HP. RESET # deve ser amarrado a VCCIO (+ 3.3V) se não estiver sendo usado.

Geradores de taxa de transmissão – Os geradores de taxa de transmissão fornecem uma entrada X16 ou X10 para o UART de um relógio de referência de 120MHz e consiste de um pré-escalador de 14 bits e 4 bits de registro que fornecem um ajuste fino da taxa de transmissão (usada para dividir por um número mais uma fração). Isso determina a taxa de transmissão do UART que é programável de 183 bauds para 12 mbaud. Veja o aplicativo FTDI Nota An_120 Aliasing Taxas de transmissão VCP para mais detalhes.

Interface EEPROM. Eeprom é opcional. Quando usado sem um EEPROM externo, o FT233HP / FT232HP é padronizado a um USB para um dispositivo de porta serial assíncrono com perfis padrão em 2 portas de 2 tipos C / PD. Adicionar um 93LC66 EEPROM externo Permite a personalização do USB VID, PID, número de série, strings de descrição do produto e valor do descritor de energia do FT233HP / FT232HP para aplicativos OEM, bem como configurações de porta PD e perfis de energia PD. Outros parâmetros controlados pelo EEPROM incluem Wake Up remoto, puxão macio para baixo na força de desligamento de energia e de E / S PIN.

O EEPROM deve ter uma ampla configuração de 16 bits, como um microchip 93lc66b ou equivalente a uma taxa de clock de 1Mbit / s no VCC = 3.0V a 3.6V. O EEPROM é programável no circuito em USB usando um programa utilitário chamado FT_PROG disponível no site da FTDI – https://www.ftdichip.com/. Isso permite que uma parte em branco seja soldada no PCB e programada como parte do processo de fabricação e teste. Se nenhum EEPROM estiver conectado (ou o EEPROM estiver em branco), o FT233HP / FT232HP será padrão para as portas seriais. O dispositivo usa seu vid padrão integrado (0403), PID (6044), descrição do produto e valor do descritor de energia. Nesse caso, o dispositivo não terá um número de série como parte do descritor USB.

Regulador LDO. O regulador LDO + 1.2V gera os volts +1.2 para o núcleo e a célula transceptor USB. Sua entrada (VREGIN) deve ser conectada a uma fonte de energia externa + 3.3V. Também é recomendado adicionar um capacitor de filtragem externo ao Vregin. Não há conexão direta a partir da saída + 1.2V (VREGOUT) e as funções internas do FT233HP / FT232HP. O PCB deve ser roteado para conectar o VRegout aos pinos que exigem o + 1.2V, incluindo Vregin.

Utmi phy. A célula de interface física do Universal Transceptor Macrocell (UTMI). Este bloco lida com a função de serdes (Serialise – Deserialise) de velocidade total / Hi-Speed para os dados USB TX / RX. Isto

Também fornece os relógios para o resto do chip. Um cristal de 12 MHz com ± 30ppm deve ser conectado ao

Osci e Os pinos de Osco ou 12 MHz Oscilador devem ser conectados ao Osci, e a OSCO não é deixada desconectada. Um resistor de 12k Ohm deve ser conectado entre a Ref e o GND no PCB.

As funções UTMI PHY incluem:

• Suporta 480 mbit / s “Hi-Speed” (HS) / 12 Mbit / s “velocidade máxima” (FS).

• Geração e verificação de sincronização / EOP

• Recuperação de dados e relógio do fluxo serial no USB.

• recheio de bits / unstuffing; bit material err ou detecção.

• gerencia o currículo USB, acorde e suspenda as funções.

• Relógio de Dados Paralelos Únicos com PLL no Chip para gerar relógios de dados de série de maior velocidade.

FT233HP / FT232HP Modo de interface UART Descrição

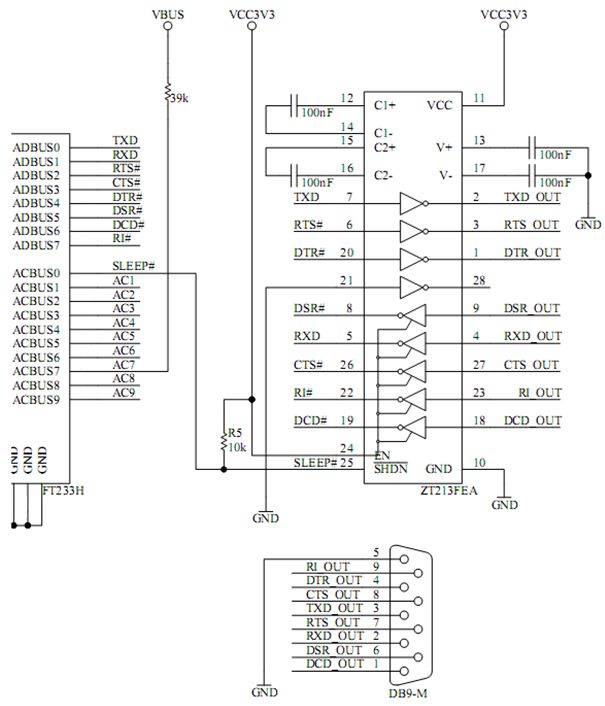

O FT233HP / FT232HP pode ser configurado como UART com drivers de linha externa, semelhante à operação com os dispositivos FTDI FT232R. Os exemplos a seguir ilustram como configurar o FT233HP / FT232HP com uma interface RS232, RS422 ou RS485.

Configuração RS232.

A Figura 5 ilustra como o FT233HP / FT232HP pode ser configurado com uma interface UART RS232.

Figura 5 – Configuração RS232

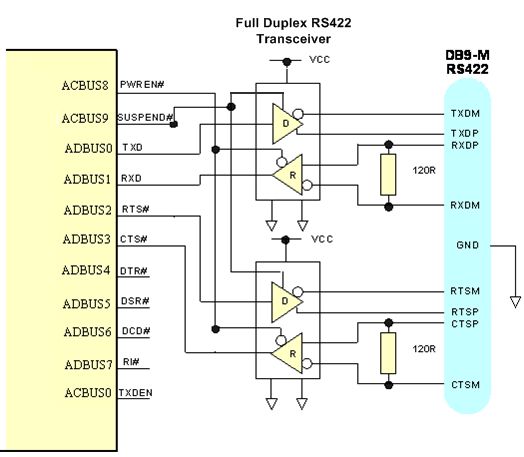

Configuração RS422.

A Figura 6 ilustra como o FT233HP / FT232HP pode ser configurado como uma interface RS422.

Figura 6 – Configuração RS422

Nesse caso, o FT233HP / FT232HP é configurado como UART operando em níveis de TTL e um dispositivo de conversor de nível (transceptor Duplex completo RS485) é usado para converter os sinais de nível TTL a partir dos níveis FT233HP / FT232HP para RS422. O sinal PWREN # é usado para ativar os shifters de nível, de modo que operam em uma corrente baixa quiescente quando a interface USB está no modo de suspensão.

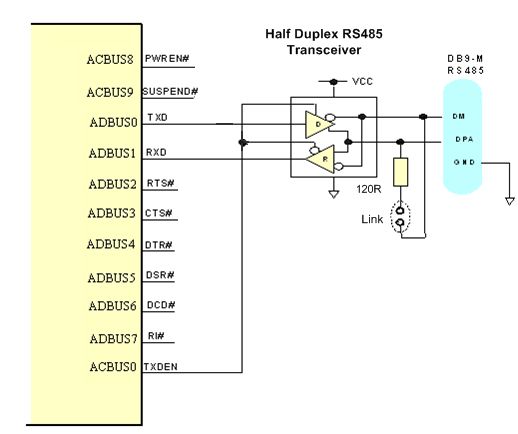

Configuração RS485.

A Figura 7 ilustra como o FT233HP / FT232HP pode ser configurado como uma interface RS485.

Figura 7 – Configuração RS485

Nesse caso, o FT233HP / FT232HP é configurado como um UART operando em níveis de TTL e um dispositivo de conversor de nível (meio transceptor RS485 duplex) é usado para converter os sinais de nível TTL dos níveis FT233HP / FT232HP para RS485. Com RS485, o transmissor só é ativado quando um personagem está sendo transmitido do UART. O PIN TXDEN no FT233HP / FT232HP é fornecido para exatamente essa finalidade, e assim o transmissor permite que sejam conectados ao TXDEN. RS485 é uma rede multi-drop – i.e. Muitos dispositivos podem se comunicar uns com os outros em uma única conexão de cabo de dois fios. O cabo RS485 requer ser terminado em cada extremidade do cabo. Os links são fornecidos para permitir que o cabo seja terminado se o dispositivo estiver fisicamente posicionado em cada extremidade do cabo.

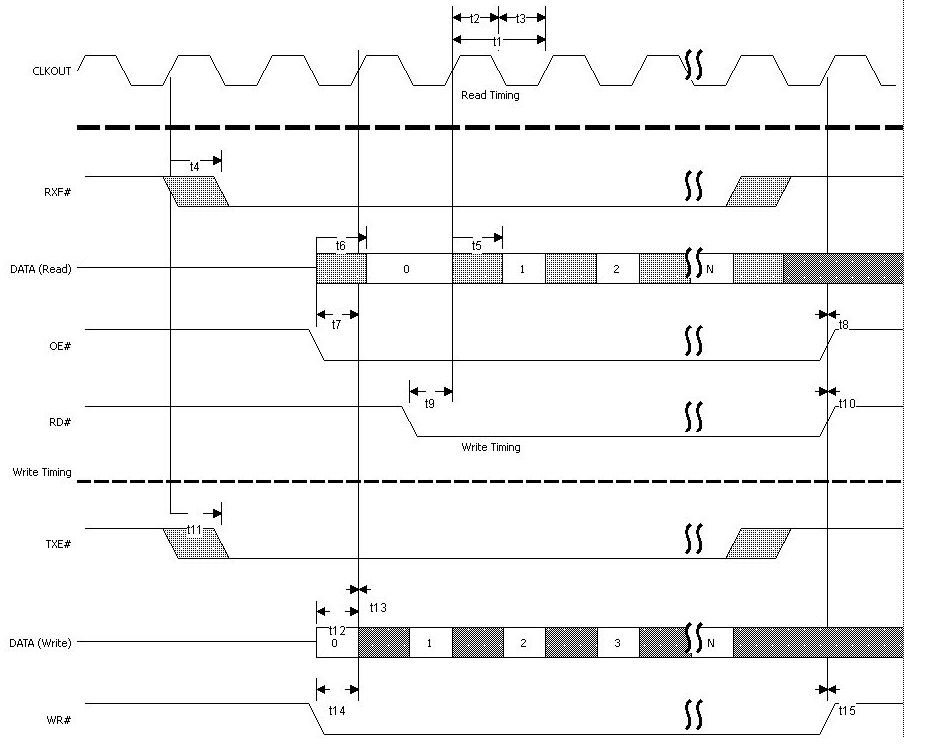

FT245 Synchronous FIFO Interface Modo Descrição

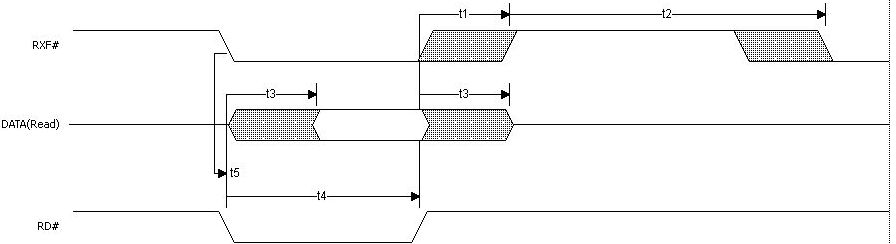

Quando o FT233HP / FT232HP estiver configurado em um modo de interface FIFO síco fifo FT245, o tempo IO dos sinais usados é mostrado na Figura 8, o que mostra detalhes para acesso a leitura e gravação. Os horários são mostrados na Figura 8. Observe que apenas um ciclo de leitura ou gravação pode ser executado a qualquer momento. Os dados são lidos ou gravados na borda crescente do relógio clkout.

Figura 8 – Formações de onda de sinal de interface FIFO Síco FT245.

| Name | Min | Nom | Max | Units | Comments |

| t1 | 16.67 | ns | CLKOUT period | ||

| t2 | 7.5 | 8.33 | 9.17 | ns | CLKOUT high period |

| t3 | 7.5 | 8.33 | 9.17 | ns | CLKOUT low period |

| t4 | 0 | 9 | ns | CLKOUT to RXF# | |

| t5 | 0 | 9 | ns | CLKOUT to read DATA valid | |

| t6 | 0 | 9 | ns | OE# to read DATA valid | |

| t7 | 7.5 | 16.67 | ns | OE# setup time | |

| t8 | 0 | ns | OE# hold time | ||

| t9 | 7.5 | 16.67 | ns | RD# setup time to CLKOUT (RD# low after OE# low) | |

| t10 | 0 | ns | RD# hold time | ||

| t11 | 0 | 9 | ns | CLKOUT TO TXE# | |

| t12 | 7.5 | 16.67 | ns | Write DATA setup time | |

| t13 | 0 | ns | Write DATA hold time | ||

| t14 | 7.5 | 16.67 | ns | WR# setup time to CLKOUT (WR# low after TXE# low) | |

| t15 | 0 | WR# hold time |

Tabela 17 – FT245 Synchronous FIFO Interface Timings.

Este modo usa uma interface síncrona para obter altas velocidades de transferência de dados. O chip dirige um relógio clkout de 60 MHz para o sistema externo a ser usado.

Observe que o modo FIFO assíncrono deve ser selecionado no EEPROM antes de selecionar o modo FIFO Síncronudo no Software.

FT245 FIFO SÍNCRO LEIA OPERAÇÃO

Uma operação de leitura é iniciada quando o chip drives rxf # baixos. O sistema externo pode então dirigir o OE # baixo para ativar os drivers de barramento de dados antes de confirmar os dados com o sinal Rd # indo baixo. O primeiro byte de dados está no ônibus depois do OE # é baixo. O sistema externo pode explodir os dados fora do chip, mantendo o RD # baixo ou ele pode inserir estados de espera no sinal Rd #. Se houver mais dados a serem lidos, ele será alterado no relógio após o Rd # amostrado baixo. Quando todos os dados foram consumidos, o chip dirige o RXF # alto. Quaisquer dados que aparecem no barramento de dados, após o RXF # é alto, é inválido e deve ser ignorado.

FT245 Synchronous FIFO Escrever Operação

Uma operação de gravação pode ser iniciada quando o TXE # é baixo. Wr # é trazido baixo quando os dados são válidos. Uma operação de burst pode ser feita em cada relógio que fornece TXE # ainda é baixa. O sistema externo deve monitorar o TXE # e seu próprio WR # para verificar se os dados foram aceitos. Tanto TXE # e WR # devem ser baixos para cada byte de dados a serem aceitos.

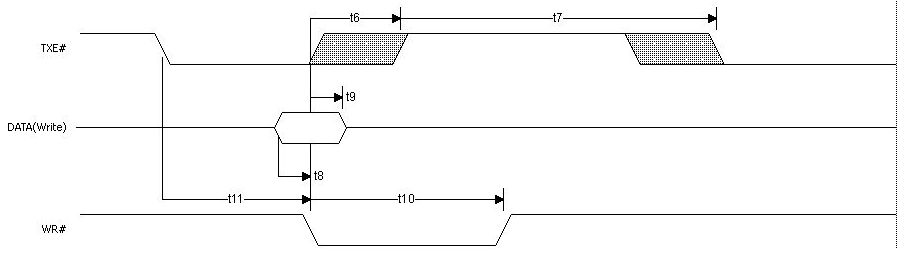

FT245 Estilo Assíncrono FIFO Interface Modo Descrição

O FT233HP / FT232HP pode ser configurado como uma interface FIFO assíncrona. Este modo é semelhante à interface FIFO síncrona com a exceção de que os dados são escritos ou lidos a partir do FIFO na borda de queda dos sinais WR # ou RD #.

Este modo não fornece um sinal clkout e não espera um sinal de entrada OE #. Os diagramas a seguir ilustram o tempo de modo de fifo assíncrono.

Figura 9 – FT245 Interface FIFO assíncrona Leia as formas de onda de sinal

Figura 10 – FT245 Asynchronous Interface FIFO Escreva formas de onda de sinal

| Time | Description | Min | Max | Units |

| T1 | RD# inactive to RXF# | 1 | 14 | Ns |

| T2 | RXF# inactive after RD# cycle | 49 | Ns | |

| T3 | RD# to DATA | 1 | 14 | Ns |

| T4 | RD# active pulse width | 30 | Ns | |

| T5 | RD# active after RXF# | 0 | Ns | |

| T6 | WR# active to TXE# inactive | 1 | 14 | Ns |

| T7 | TXE# active to TXE# after WR# cycle | 49 | Ns | |

| T8 | DATA to WR# active setup time | 5 | Ns | |

| T9 | DATA hold time after WR# inactive | 5 | Ns | |

| T10 | WR# active pulse width | 30 | Ns | |

| T11 | WR# active after TXE# | 0 | Ns |

Tabela 18 – Tempo de FIFO assíncronos (com base nas saídas de nível de unidade padrão)

Última atualização em fevereiro 16, 2024 por driverbr

Deixe um comentário