Introdução

O FT2232H e FT4232H são a primeira velocidade USB 2.0 da FTDI (480MBits / s) USB para UART / FIFO. Eles também têm a capacidade de ser configurado em uma variedade de interfaces seriais usando o MPSSE interno (motor serial síncrono multi-protocolo). O dispositivo FT2232H possui duas portas independentes, ambas as quais podem ser configuradas usando o MPSSE enquanto apenas canal A e B de FT4232H podem ser configurados usando o MPSSE.

O uso de MPSSE pode simplificar o protocolo serial síncrono (USB para SPI, I2C, Jtag, etc.). Esta nota de aplicativo ilustra como usar o MPSSE do FT2232H para interface com o barramento I2C. Os usuários podem usar o exemplo de código de software esquemático e funcional para começar seu design. Observe que o código de software é fornecido apenas como uma ilustração e não suportado pelo FTDI.

Introdução do ônibus I2C.

O I2C é um barramento de comunicação mestre / escravo de taxa de data média e média. Dois fios, dados seriais (SDA) e relógio serial (SCL), transportar informações entre os dispositivos conectados ao barramento. Cada dispositivo é reconhecido por um endereço exclusivo e pode operar como um transmissor ou receptor, dependendo da função do dispositivo. Além de transmissores e receptores, os dispositivos também podem ser considerados mestres ou escravos ao realizar transferências de dados. Um mestre é o dispositivo que inicia uma transferência de dados no barramento. Naquela época, qualquer dispositivo endereçado é considerado um escravo.

A camada física do barramento I2C é um protocolo de handshaking simples que depende de saídas de coletor aberto nos dispositivos de barramento e ao dispositivo dirigindo ou liberando as linhas de barramento, portanto, um resistor de pull-up é necessário em cada fio do barramento.

O Ônibus do I2C é um verdadeiro barramento multi-mestre, incluindo detecção de colisão e arbitragem para evitar a corrupção de dados se dois ou mais mestres iniciaram simultaneamente a transferência de dados

Transferências de dados bidirecionadas em série, de 8 bits, podem ser feitas em até 100 kbit / s no modo padrão de barramento I2C, até 400 kbit / s no modo rápido ou até 3,4 mbit / s em o modo de alta velocidade.

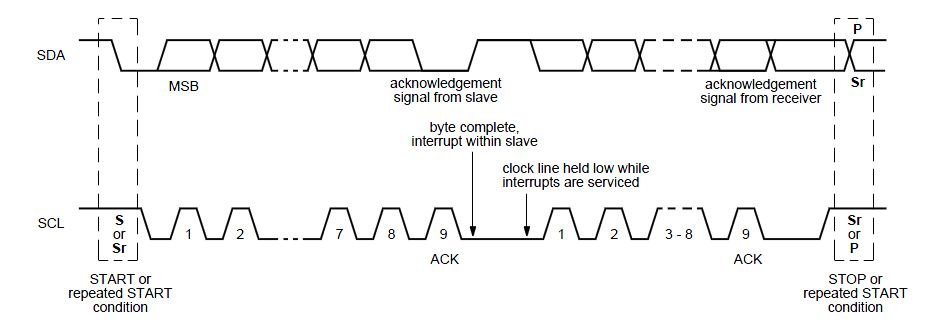

A Figura 1 mostra transferências de dados típicas no barramento I2C. O mestre fornece o relógio; Inicia e termina as transações e o escravo pretendido (com base no endereço fornecido pelo mestre) reconhece o mestre dirigindo ou liberando o barramento. O escravo não pode terminar a transação, mas pode indicar um desejo de um “nak” ou não reconhecido.

Figura 1 Transferência de dados no barramento I2C

A especificação i2c define situações únicas como condições de partida e parada (p) (veja a Figura 2). Uma transição alta para baixa na linha SDA enquanto a SCL é alta indica uma condição de início. Uma transição baixa a alta na linha SDA enquanto a SCL é alta define uma condição de parada. As condições de início e parada são sempre geradas pelo mestre.

Figura 2 Condições de início e parada

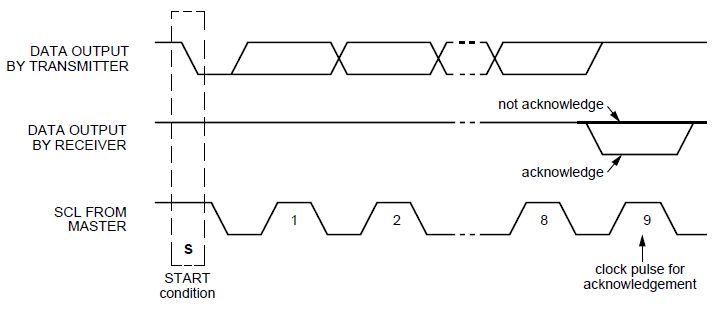

Cada byte colocado na linha SDA deve ter 8 bits de comprimento. O número de bytes pode ser transmitido por transferência é irrestrito. Cada byte é seguido por um bit de reconhecimento. Os dados são transferidos com o bit mais significativo (MSB) primeiro. Na maioria dos casos, a transferência de dados com reconhecimento é obrigatória. O pulso de relógio relacionado ao reconhecimento é gerado pelo mestre. O transmissor libera a linha SDA (alta) durante o pulso do relógio de reconhecimento. O receptor deve reduzir a linha SDA durante o pulso do relógio de confirmação para que ele permaneça estável baixo durante o alto período deste pulso de clock (veja a Figura 3). Além disso, a configuração e os tempos de espera também devem ser levados em conta.

Figura 3 Reconheça o I2C-BUS

Transferências de dados da especificação I2C devem seguir o formato. Após a (s) condição (s) de início, um endereço escravo deve ser enviado primeiro. Este endereço é de 7 bits seguidos por um oitavo bit que é um bit de direção de dados (R / W̅) – A ‘zero’ indica uma transmissão (gravação), um ‘um’ indica uma solicitação de dados (leitura). Depois que o byte do endereço escravo for enviado, o mestre pode continuar sua transferência de dados, escrevendo ou lendo byte de dados como formato definido. A transferência de dados é sempre encerrada por uma condição de parada gerada pelo mestre.

Projeto de amostra com FT2232H

Visão geral

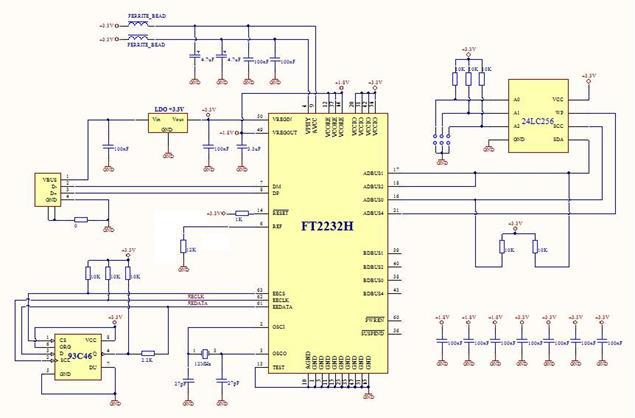

Para demonstrar como usar o mecanismo serial síncrono multi-protocolo (MPSSE) em uma interface de barramento USB para I2C, é dado um projeto de amostra. Um dispositivo EEPROM (24LC256) com interface serial I2C é selecionado como a aplicação típica. Um esquema de referência mostrando a conexão I2C entre o FT2232H e o 24LC256 é dado. Além disso, alguns softwares de amostra (listagem C ++) são fornecidos, o que ilustra como inicializar, programar e ler um dispositivo de 24LC256 EEPROM através da interface I2C.

Circuito de amostra

Figura 4 Interface FT2232H com 24LC256

A Figura 1 ilustra um exemplo de interface da porta de MPSSE de FT2232H com dispositivo EEPROM serial I2C. O FT2232H está em Configuração de Design Powered do Barramento USB. Por favor, consulte a folha de dados FT2232H para especificações detalhadas. O USB VBUS (+ 5V) é regulamentado para + 3.3V para fornecer VCCIO, VPHY, VPLL e Vregin de FT2232H, o 93C46 EEPROM e os dispositivos de 24LC256 EEPROM. A saída do regulador LDO ON-Chip (+ 1.8V) de FT2232H impulsiona a fonte de núcleo FT2232H (VCORE). O 93C46 EEPROM é uma opção para permitir a personalização de configurações USB, como VID / PID, descrição, número de série, despertar remoto, etc.

Um eeprom serial de microchip 24lc256 é usado como dispositivo de destino. O 24LC256 é um baile de 256K Bits eletricamente apagável com interface serial compatível com 2 fios I2C. Suporta uma frequência de relógio serial de até 400 kHz. Por favor, consulte a folha de dados de 24LC256 para uma especificação detalhada.

Os pinos A0, A1, A2 são usados pelo dispositivo 24LC256 para várias operações de dispositivos. O chip é selecionado quando os níveis dessas entradas são idênticos ao endereço escravo. Eles podem ser vinculados a vcc ou vss no circuito acima.

Ambos os canais de FT2232H podem ser configurados para trabalhar no modo MPSSE. O canal A é usado na figura 1. As definições detalhadas do pino para a conexão I2C FT2232H são descritas na tabela 1. Uma descrição funcional detalhada é dada abaixo:

SK – Conecte-se ao Pin SCL de 24LC256. Pin do relógio serial para sincronizar a transferência de dados, iniciada por FT2232H e saída para 24LC256. O valor do relógio é determinado pelo divisor de relógio interno FT2232H e pode ser de até 30 MHz, este sinal requer um resistor de pull-up para o VCC (típico 10 kΩ para 100 kHz e 2 kΩ para 400 kHz).

Faça / di-wired juntos e conectado ao Pin SDA de 24LC256 para transferência de dados bidirecional. Defina como PIN de saída para transferir dados seriais ou endereço do dispositivo FT2232H para 24LC256. DI definido como pino de entrada para receber o PIN de entrada de dados seriais do dispositivo de 24LC256 para FT2232H. Requer um resistor pull-up para o VCC (típico 10 kΩ para 100 kHz e 2 kΩ para 400 kHz).

GPiol0 – E / S de propósito geral da porta de MPSSE de FT2232H. Conecte-se ao pino WP do dispositivo de 24LC256 para controlar a função de proteção de gravação do dispositivo 24LC256. Isso é definido para um nível baixo lógico para o modo de operação normal do 24LC256. Se definido para um nível de alta lógica, a operação de gravação do dispositivo 24LC256 será proibida.

| Channel A | Channel B | MPSSE

Pin Name |

Type | Description | ||

| Pin# | Pin Name | Pin # | Pin Name | |||

| 16 | ADBUS0 | 38 | BDBUS0 | SK | Output | Serial Clock |

| 17 | ADBUS1 | 39 | BDBUS1 | DO | Output | Serial Data/Address Output |

| 18 | ADBUS2 | 40 | BDBUS2 | DI | Input | Serial Data Input |

| 21 | ADBUS4 | 43 | BDBUS4 | GPIOL0/ GPIOH0 | Output | Write Protect control output |

Tabela 1 Descrição de FT2232H Conectando com 24LC256

Última atualização em fevereiro 16, 2024 por driverbr

Deixe um comentário